FPGA-HLS

FPGA-HLS

一、HLS(High Level Synthesis)简介

1.1 什么是HLS

HLS是Xilinx公司推出的一个开发工具,其可以将C/Cpp/System C代码进行C域综合,并将其转换成Verilog/HDL语句,最终可以将其逻辑功能与接口打包生成IP核,供后续FPGA开发使用。

1.2 为什么要用HLS做IP核开发

加速设计开发的周期:

首先,很多设计原本就是使用C或者C++来设计的,算法移植的时候,如果每次都要重新按照C来写verilog,会复杂且不稳定,而且需要开发人员同时掌握这两种语法。

其次,使用HLS是“抽象层级的提升”,等于创建了一个黑箱工程,里面怎么操作开发人员不用管,只需要确保C的逻辑正确即可。

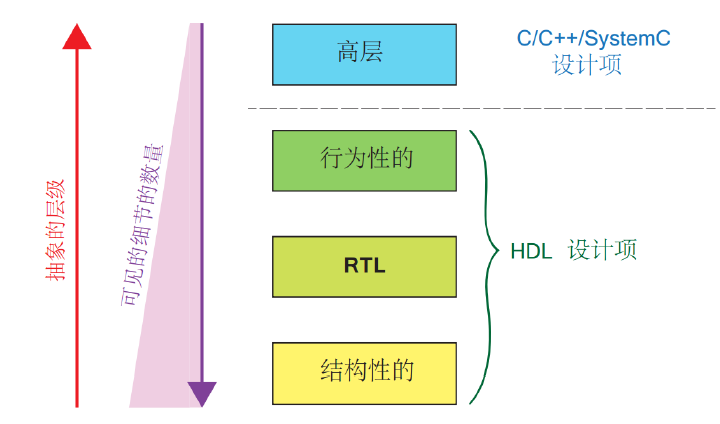

如图所示,FPGA设计从底层向上一共是四层抽象层级:结构性、RTL、行为性、高层。

其中最底层的结构性,包含各种底层硬件单元,比如逻辑门、LUT、触发器等等。

像我们经常做的Vivado中的Verilog开发,即是第二层RTL层开发,这个层级会隐藏底层的细节。

更上层的行为性的开发,是对电路的算法描述,也就是描述电路表现出什么样的功能,而不是描述具体某个寄存器的操作。

可以看出,随着抽象层级的提升,设计最终在硬件上实现的细节逐渐被弱化。

1.3 HLS设计流程

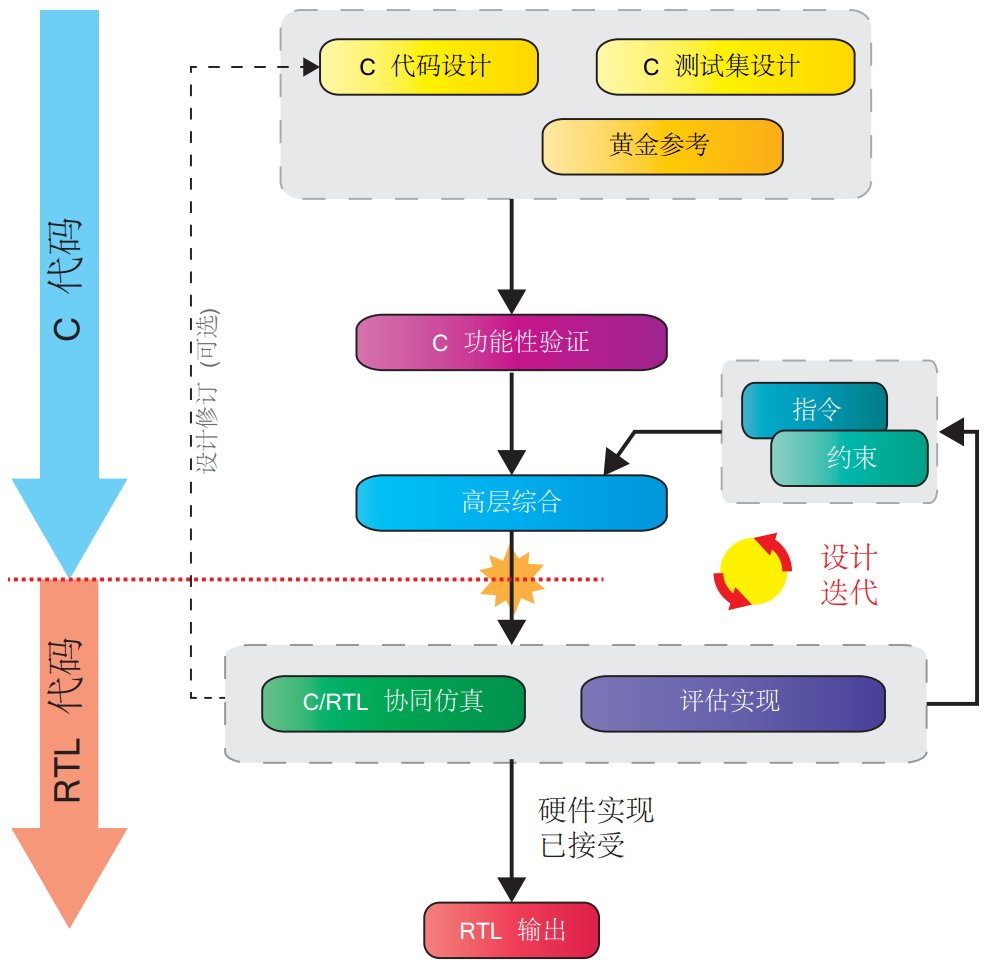

下面是HLS设计的流程图:

可以看到

1.4 接口综合方法

1.5 算法综合方法

1.6 HLS库

二、通过按键控制LED灯实验学会HLS设计流程

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 JERRY'S BLOG!