超声系统&高速采集设备

xx 等长

xxx 为什么要做等长

核心结论:AFE 前的信号本质上处在相对低频的模拟域,走线相位差与波长相比微不足道;AFE 后进入高速数字域(例如 LVDS/SerDes),走线差直接转化为采样时序偏差,超过眼图开口会导致位错与码错。

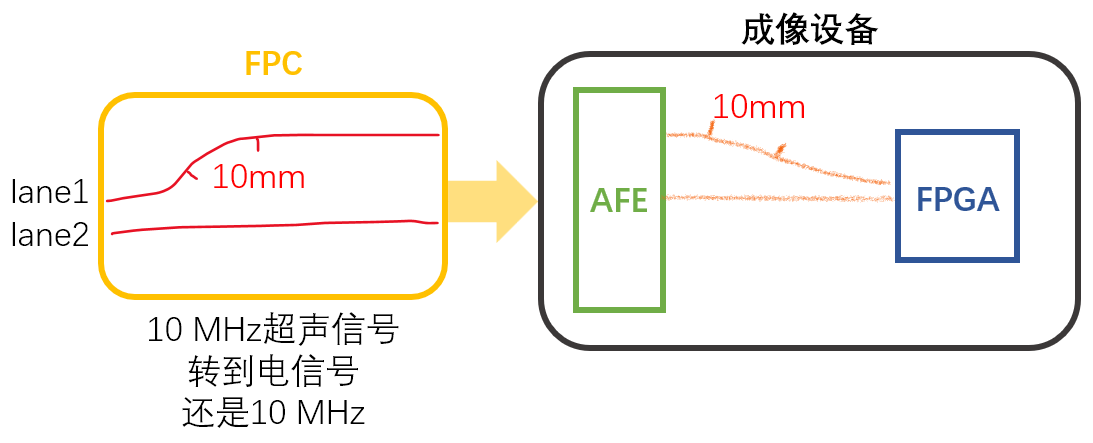

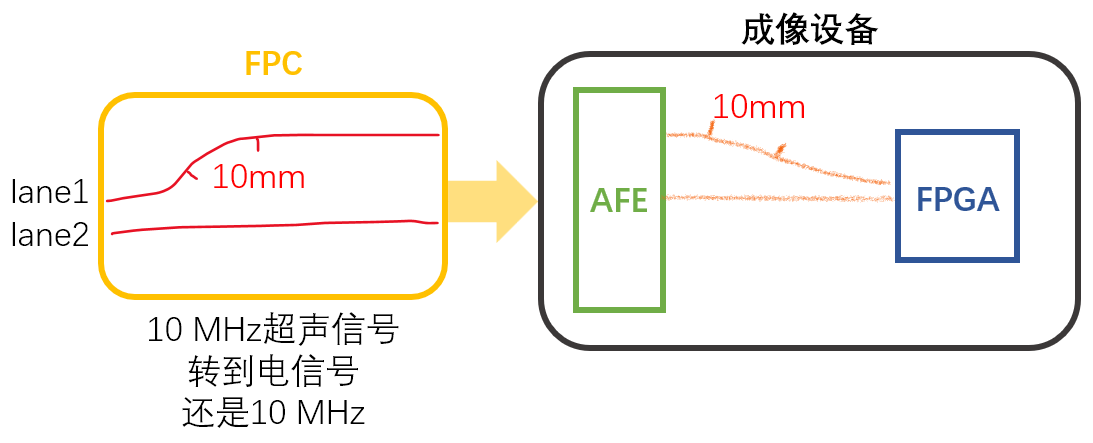

假设图上这样一个超声采集成像设备,前面是FPC电路,后面是成像设备,先通过AFE模拟转数字,再将数字信号传入到FPGA中。

在 PCB 介质中,电磁波速度约为 v≈εeffc。以 FR-4 为例,εr≈4.2∼4.8,故 v≈(1.4∼1.6)×108 m/s。

波长 λ 与频率 f 的关系为 λ=fv。

AFE 之前(模拟域):10 mm 线差几乎不构成问题

在这套系统中,换能器→FPC→AFE 之前的有效电信号等价于声学 10 MHz 的窄带模拟信号。

取 v=1.5×108 m/s、f=10 MHz,则

- 波长:λ=fv=1071.5×108=15 m;

也就是说,10 mm 的不等长相较 15 m 的波长几乎可忽略。它顶多在波束形成(DAS)时造成极轻微的相位不一致,表现为点扩散函数(PSF)略有展宽、图像分辨率几乎不可感的下降;而这类“慢变化、全通道可校”的误差,本就可以在延时—求和的数字域标定中补偿。

注意:AFE 前虽然不用“强制等长”,但仍需重视阻抗连续、屏蔽与串扰、回流路径完整性等模拟布线要点——这些往往比“等长”更关键。

AFE 之后(数字域):同样的 10 mm 线差可能直接导致码错

假设 AFE→FPGA 采用 16 路 LVDS + 时钟,时钟 fclk=480 MHz,双沿采样等效数据率约 f≈960 MHz,便于估算按 1 GHz 计:

- 波长:λ=fv=1091.5×108=0.15 m=15 cm;

若两通道线差达到 15 cm,恰好 相差 1 个周期,会导致“位正好错周”的灾难性错误(例如符号位错位,1111 1111 的最高位极性全错)。更现实的是,高速链路眼图并非满开口,有效采样窗口常仅有 ∼0.1 T。据此可得最大可容许线差

ΔLmax≈v×(0.1T)=f0.1v≈1.5 cm.

也就是说,超过约 1.5 cm 的不等长就可能让采样落在错误边沿或噪声区,出现错位、码错甚至链路无法锁定。更高速的 SerDes/PCIe下,亚毫米级的不等长都可能触发错误;工程上常见“对内不等长 5 mil(0.127 mm)也要小心”的提示,正源于此。

那么如何给等长做预算?

把“链路可容忍时序偏差”转成走线预算即可:

ΔLmax=v⋅Teye,Teye=α⋅f1, (0<α<1)

其中 α 为眼图开口比例(含抖动、ISI、抖动余量、采样保持、封装与连接器不确定性等)。

- AFE 前(模拟):无需追求通道等长,更关注阻抗匹配(同轴/差分对)、回流路径、跨层过孔、屏蔽与串扰控制;多通道相位差由数字延时校准统一补偿。

- AFE 后(数字):

- 对内(intra-pair):差分对正负线极严格等长,工程上常控制在 <5 mil;

- 对间/数据-时钟(inter-pair):除等长再留安全余量(连接器、封装、走线工差、温漂)。 你的原文记录(未删减)

以上是AI生成的,下面是我发给AI的提示词

1

2

3

| 我有一个超声成像系统,连接AFE前有超声换能器+FPC电路,AFE后有电路流到FPGA中,我以前都没搞懂为什么AFE前不用做电路等长,但是AFE后就要做电路等长,后面我搞明白了,假设AFE前有10mm的线差,AFE后也有10mm的线差,这10mm的线差在AFE之前,会导致两根线之间的延迟不同,假设都按照FR4 PCB的介电常数来计算,电信号v=1.5*10^8m/s超声信号被换能器采集后传输至FPC中,假设这个超声信号(声学)是f=10MHZ,那他转化成电信号也是10Mhz,波长就是v/f=1.5*10^8m/s / 10Mhz = 15m,这小小的10mm没有等长相比这么大的波长,不值一提,不会产生很大影响,而且哪怕有一些影响,也只会影响最终DAS波束形成结果(增大一点点点PSF)和物理意义上的理论结果不一致,产生图像分辨率稍微低一点点点。

但是如果是AFE之后,也就是变成数字电路后,等长差10mm,那就会产生很大的影响,假设使用lvds来进行16路的数字信号传输,使用一个时钟,时钟频率为480MHz,然而由于lvds采样使用时钟上下沿都采样,因此实际采样频率为960MHz,我们假设就是1GHz方便计算,此时电信号依旧v=1.5*10^8m/s,此时波长为v/f=1.5*10^8m/s / 1*10^9Hz=0.15m,也就是说,如果在一个时钟上升沿,两通道信号线差大于15cm,此时两个通道被时钟采的信号正好相差1个周期,这会导致很大的问题,比如1111 1111,第8位如果是正负标志位,那一个信号没对齐,后面正负都直接错了。更恐怖的是这只是理想情况下,在实际情况下还要考虑眼图的问题,对于一个质量不佳的高速信号,可采集的区域范围也许只有0.1个时钟周期,也就是说,线差如果大于1.5cm,那可能就会产生采回来的信号是错的,或者是错位的。

当然serdes和PCIE等的速度更快,一点点的甚至5个mil=0.127mm的线差都可能导致数据错位,以上就是为什么要做等长,和为什么等长在AFE之前(或者可以说在模拟信号转成数字信号之前)都是无所谓的,但是在AFE之后(或者可以说变成高速数字信号之后)就非常重要且关键了!

|