Vivado操作备注

Vivado操作备注

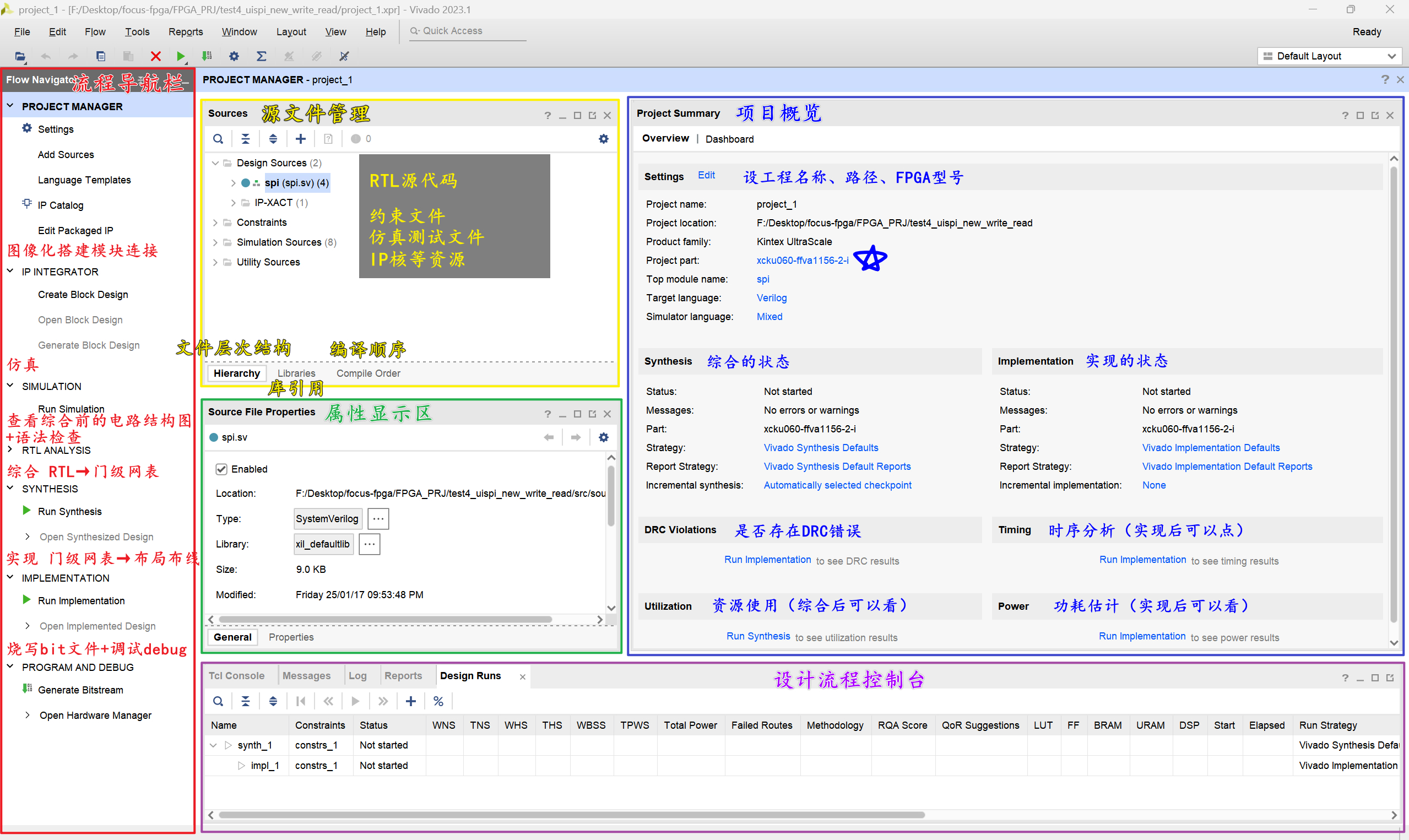

一、Vivado操作界面

二、Vivado工程整体工作流程及其对应仿真

Vivado一整个工程整体流程如下:

| 第一步 | 第二步 | 第三步 | |

|---|---|---|---|

| 工程流程 | 写.v /.sv文件用于实现电路逻辑 |

Run Synthesis(综合) 将代码转成门级网表 |

Run Implementation(实现) 将门级网表转成FPGA中的电路,即布局布线 |

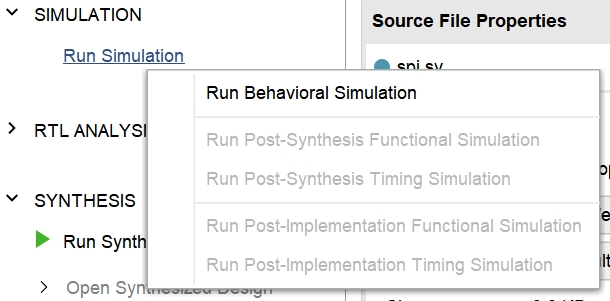

| 功能仿真 (不含延迟) |

Run Behavioral Simulation (验证 RTL 原始功能) |

Run Post-Synthesis Functional Simulation (验证综合后功能未改变—不带电路延迟) |

Run Post-Implementation Functional (验证实现后功能未改变—不带电路延迟) |

| 时序仿真 (含延迟) |

无(RTL 无延迟信息) | Run Post-Synthesis Timing Simulation (验证综合后是否满足时序—带电路延迟) |

SimulationRun Post-lmplementation Timing Simulation (验证最终实现是否满足时序—带电路延迟) |

可以看到最重要的就是实现电路逻辑,之后综合和实现软件可以自动实现,在综合和实现后进行仿真进行逻辑时序确认。

对于Vivado中的各种仿真,有不小的区别:

| 仿真类型 | 输入来源 | 是否包含时延 | 主要目的 | 典型应用阶段 |

|---|---|---|---|---|

| Behavioral Simulation | RTL代码 | 否 | 验证功能逻辑 | 初始开发 |

| Post-Synthesis Functional | 综合后的网表 | 否 | 验证综合后功能是否正确 | 综合后 |

| Post-Synthesis Timing | 网表 + 综合时延 | 是 | 初步验证时序逻辑 | 时序分析前 |

| Post-Implementation Functional | 布局布线后的网表 | 否 | 验证最终实现逻辑 | 实现后 |

| Post-Implementation Timing | 网表 + 精确时延 | 是 | 完整时序验证,签核阶段 | 收尾 |

因此对于小型模块或代码的仿真,可以直接用Post-Synthesis Functional来进行,验证功能逻辑ok即可;而对于大型模块或代码的仿真,则需要使用Post-Implementation Timing来进行最终时序的仿真,确保万无一失。

三、Block Design的使用与否

3.1 什么是Block Design

3.2 何时用Block Design

| 项目规模 | 建议做法 |

|---|---|

| 小项目 | 继续纯 RTL,不用 BD,快速灵活 |

| 中大型项目(Zynq / AXI) | 用 BD 搭框架(PS + DMA + AXI),然后把你自己的算法模块 Add Module 进去 |

| 需要交给团队协作 | 建议 BD,图形化方便其他人接手 |

| 项目维度 | 纯 RTL 方式 | Block Design 方式 |

|---|---|---|

| 顶层结构 | 手写 .v 顶层 | Vivado 自动生成 .bd + wrapper |

| IP 加入 | 手动例化 .xci |

拖拽 + 自动连接 |

| 模块连接 | 全手工连线 | 图形化、可自动完成 |

| 工程复杂度 | 简单逻辑很方便 | 复杂系统(AXI)更高效 |

| 控制粒度 | 完全自己控制 | 顶层被 Vivado 生成,定制灵活度略低 |

| 调试维护 | 更适合熟练开发者 | 更适合系统集成和团队协作 |

| 重用性 | 自己组织 | Vivado 提供 Reuse BD 的机制 |

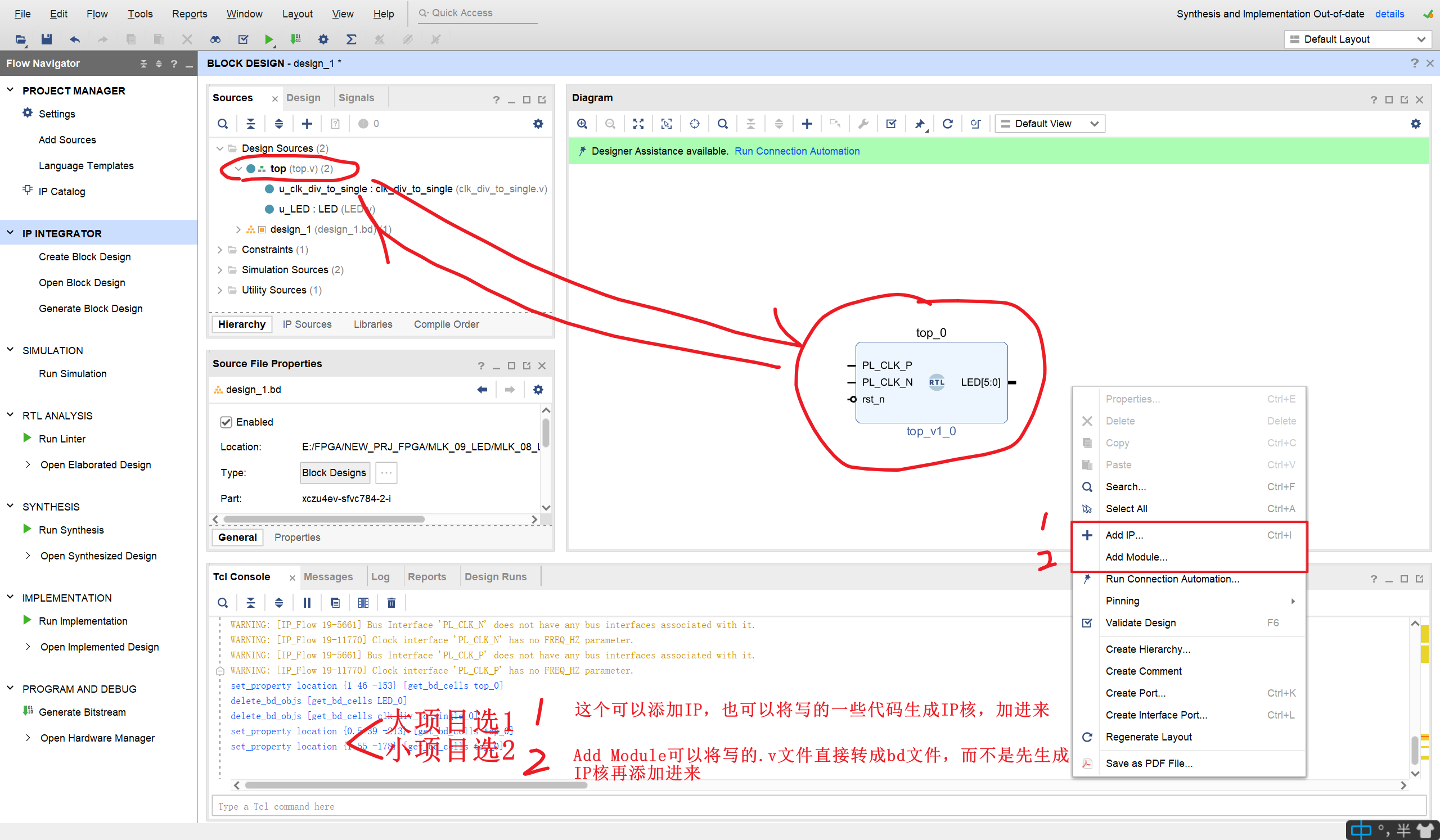

3.3 BD文件添加内容

对于Block Design,有两种方法向BD文件添加块内容,第一种是Add IP,另一种是Add Module:

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 JERRY'S BLOG!